最后编辑于: 2011-08-16 15:11 | 分类: FPGA | 标签: | 浏览数: 1074 | 评论数: 0

这是当年(2011.08.16)搜集的2篇文章, 揉在一起了.

可惜原文的链接如今搜索了蛮久都没找到.

一、提高设计的工作频率

二、获得正确的时序分析报告(STA:静态时序分析)

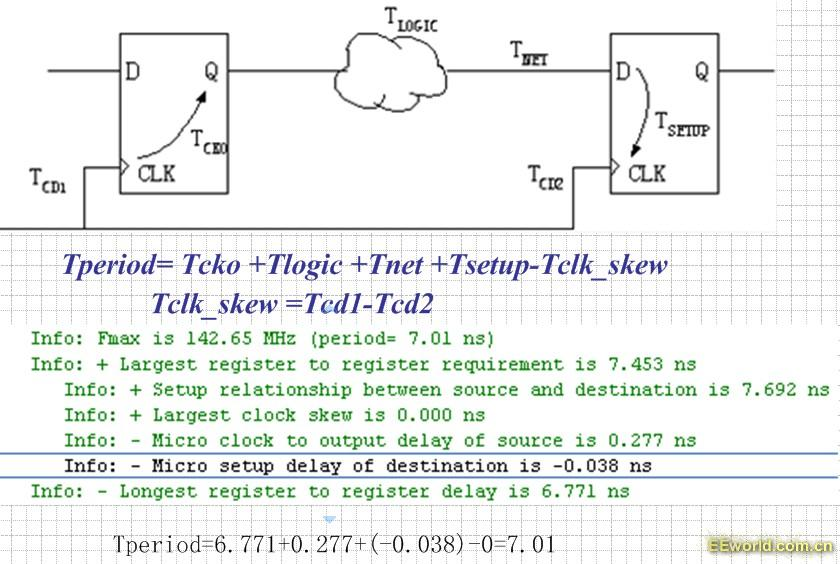

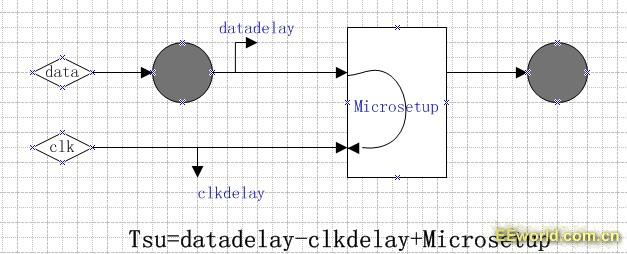

Tperiod, 那么当然fmax=1/Tperiod, fmax是显示设计最重要的性能指标之一。Th = clkdelay - datadelay + Microhold注意:前两个公式中提到的Microsetup和Microhold一般均是一个小于1ns的常量。

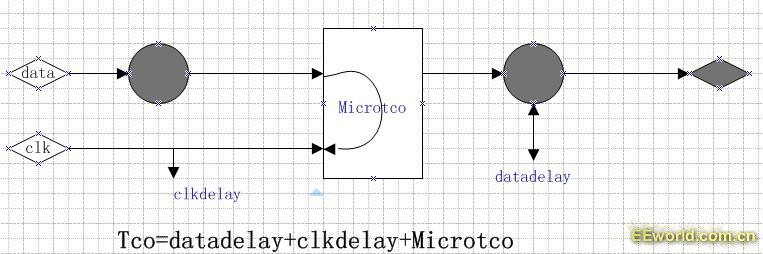

Tco = clkdelay + datadelay + Microco

图1 Tperiod的计算公式

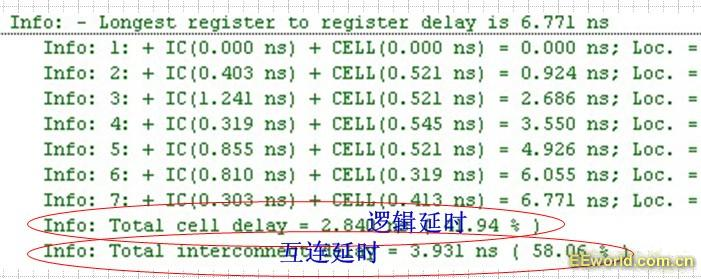

图2 逻辑延时与互连延时

图3 时钟建立时间计算

图4 时钟输出延迟 计算方法

常用的三种时序约束设置方法:

Assignment/timing settingsAssignment/timing wiard toolAssignment/Assignment editor选择在图形界面下完成对设计的时序约束。一般情况下前两种是做全局的时序约束,后一种是做局部的时序约束,另外还可以通过修改.qsf文件来实现。

时序约束一般都是先全局后个别,如果冲突则个别的优先级更高。

一、将编绎器设置为时序驱动编绎

即是指让编绎过程尽量向着满足时序约束方向努力!assignment/settings/fitter setting.

二、全局时钟设置

如果在设计中只有一个全局时钟,或者所有的时钟同频,可以在Quartus2中只设置一个全局时钟约束。Assignment/timing settings

三、时序向导

在对时序约束设置不熟悉的情况下,可以选择使用向导。 Assignment/classic timing analyser wizards.

四、可以设置独立时钟与衍生时钟

衍生时钟是由独立时钟变化而来的,他是由独立时钟分频,倍频,移相等变化而来的,可以在设置中确定二者的关系 Assignment/settings/timing analyse setting/classic timing analyse setting/individual clock。

五、通过assignment editor设置个别时钟约束

后记: 下面是当年博文下一个朋友的留言

sherley @2016-06-15 15:58 看了所有FPGA的日志,帮助很大,这都五年前的记录,可惜大侠已经转方向了,好人啊 干实事的人....

倍感欣慰和骄傲, 也是我的动力!